# Help Volume

© 1998 Hewlett Packard Company. All rights reserved.

Instrument: HP 16522A 200 MHz Pattern Generator

# Using the HP 16522A Pattern Generator

The HP 16522A Pattern Generator is used by digital design teams to emulate digital signals in circuits under development. The pattern generator can take the place of missing devices, or can act as a stimulus to functionally test prototypes.

#### **Getting Started**

- "Overview of the HP 16522A Pattern Generator" on page 12

- "A Beginner's Exercise" on page 19

#### **Creating the Program**

- "Building an Initialization Sequence" on page 22

- "Building a Main Sequence" on page 24

- "Building a User Macro" on page 26

- "Importing HP 16522A ASCII Files" on page 29

- "Importing System Data Files" on page 40

- "Loading and Saving Pattern Generator Configurations" on page 43

#### See Also

- "Selecting the Correct Probe Pod" on page 44

- "Connecting the Probe Pods" on page 48

- "Editing Sequences" on page 50

- "Working with Instruction Types" on page 56

- "Working with Labels and Pods" on page 66

- "Working with Macro Parameters" on page 79

- "Working with Automatic Pattern Fills" on page 82

- "Loading and Saving Pattern Generator Configurations" on page 43

- "Printing the Pattern Generator Window" on page 89

- "Printing Vector Sequences to a File" on page 90

"Viewing a Compiled Sequence" on page 101

Using the Intermodule Window (see the *HP 16600A/16700A Logic Analysis System* help volume)

"Theory of Operation" on page 92

"Key Characteristics" on page 95

"Testing the Pattern Generator Hardware" on page 102

"Help - How to Navigate Quickly" on page 104

Main System Help (see the HP 16600A/16700A Logic Analysis System help volume)

Glossary of Terms (see page 111)

### Using the HP 16522A Pattern Generator

### 1 Using the HP 16522A Pattern Generator

Overview of the HP 16522A Pattern Generator 12

Mapping Probe Pods to the Interface 13

Vector Output Mode 14

Clock Source 15

Building a Sequence of Test Vectors 17

Running the Pattern Generator 18

A Beginner's Exercise 19 Configure Format 19 Configure Sequence 20 View the Results 21

Building an Initialization Sequence 22

Building a Main Sequence 24

Building a User Macro 26

Importing HP 16522A ASCII Files 29 Creating an ASCII File 31 ASCII Disk File Identifier 33 ASCII File Commands 33

Importing System Data Files 40 Data Sets 41 Data Set Labels 41 Data Set Range 42

Loading and Saving Pattern Generator Configurations 43

Selecting the Correct Probe Pod 44

## Connecting the Probe Pods 48

Editing Sequences 50

Cutting, Copying, Pasting, and Deleting Sequence Lines 50

Deleting Sequence Lines 51

Inserting Blank Sequence Lines 53

Go to a Line Number 53

Positioning the Sequence 54

Using Ditto "values 54

Working with Instruction Types 56

The Break Instruction 57

The Signal IMB Instruction 58

The Wait IMB Event Instruction 58

The Wait External Event Instruction 59

The If External Event Instruction 60

The If IMB Event Instruction 61

The User Macro Instruction 63

The Repeat Loop Instruction 64

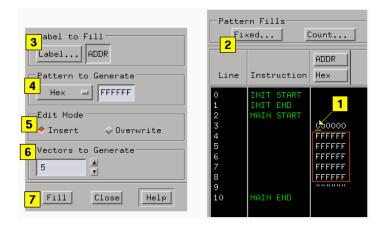

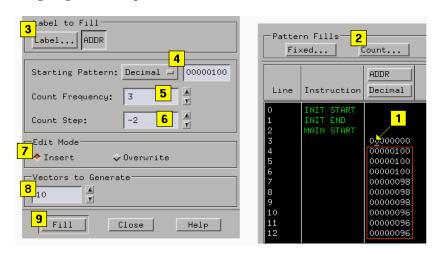

Creating and Inserting New Labels 67 Deleting Labels 68 Inserting Pre-assigned Labels Renaming Existing Labels 69 Reordering a Label's Pod Bits 70 Turning Labels On/Off 70 Clearing Format Labels 71 Searching for Labels 71 Swap Pods 71 Clear Pods 72 Assigning Bits to a Label Label Polarity 73 Finding a label 73 Replace Labels 75 Appending Labels Insert All Labels 76 Delete All Labels 76 Setting the Label Font Size 76 Adjusting Column Width 77 Setting Column Color 77 Setting the Numeric Base 78 Rearranging the Label Order 78 Working with Macro Parameters 79 Turning Parameters On 79 Inserting Parameters into a Macro 80 Assigning Parameter Values 80 Removing Parameters from a Macro 81 Working with Automatic Pattern Fills Generating a Fixed Pattern Fill Generating a Count Pattern Fill Generating a Rotate Pattern Fill Generating a Toggle Pattern Fill Generating a Random Pattern Fill 87

Working with Labels and Pods

Printing the Pattern Generator Window 89

Printing Vector Sequences to a File 90

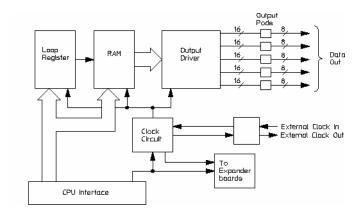

Theory of Operation 92

Loop Register PGTheory 92

RAM PGTheory 93

Output Driver PGTheory 93

Clock Circuit PGTheory 93

CPU Interface PGTheory 94

Clock and Data Pod PGTheory 94

Key Characteristics 95

Automatic Cursor Wrap 97

Recalling Macros 98

Copying Macros 100

Viewing a Compiled Sequence 101

Testing the Pattern Generator Hardware 102

Help - How to Navigate Quickly 104

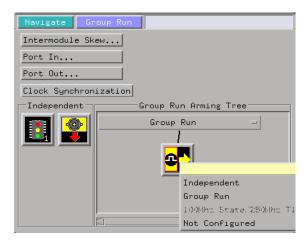

Run/Group Run Function 105

Setting a tool for independent or Group Run 106

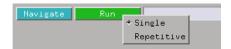

Setting Single or Repetitive Run 107

Checking Run Status 107

Demand Driven Data 108

# Glossary

Index

1

Using the HP 16522A Pattern Generator

## Overview of the HP 16522A Pattern Generator

### **Description of the HP 16522A Pattern Generator**

The HP 16522A Pattern Generator is a tool that generates digital signals. It is used in applications that require an external source to simulate digital circuitry or generate digital signals for functionally testing prototype hardware.

Combined with the analog and digital measurement capabilities of the logic analysis system, you have a tightly integrated solution to your digital stimulus and response measurement needs.

#### **A Conceptual Measurement Example**

The exact output pattern, clock type and speed, and number of required signals depends on your specific application. How you configure the pattern generator and what kind of signal generation sequence you create will vary. However, from a procedural standpoint, the steps are the same each time to set up, create a sequence, and run the pattern generator.

- 1. Select the probing (see page 44) that is compatible with your target circuit.

- 2. Set the Vector Output mode (see page 14) and the Clock Source (see page 15) parameters.

- 3. Connect the probes (see page 48) to your circuit and map the probe channels (see page 13) into the interface of the pattern generator.

- 4. Build a sequence of test vectors (see page 17) to generate the desired output signals.

- 5. Run (see page 18) the pattern generator and measure the active target circuit or prototype for the desired results.

## **Re-using Pattern Generator Programs**

After you set up a pattern generator configuration, you may want to store it away so you can use it again. Perhaps you want to create a set of test routines or circuit simulators. There are two ways to handle reusable configurations.

- You can reload previously saved (see page 43) pattern generator configurations.

- You can import an HP 16522A ASCII file (see page 29)

#### See Also

"A Beginner's Exercise" on page 19

"Theory of Operation" on page 92

"Key Characteristics" on page 95

"Help - How to Navigate Quickly" on page 104

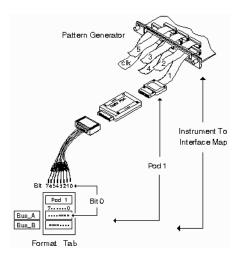

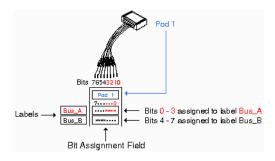

# Mapping Probe Pods to the Interface

While the probes make the physical connection to your target circuit, a software connection is also made within the interface which routes generated signals to the proper probe output lines. This software connection is done within the Format tab and is called mapping.

The mapping process consists of logically grouping output signals that have a similar purpose to a label (see page 66) with a unique name. To add to or delete signals from a group, you simply turn On/Off the bits (see page 72) beside the label.

#### **Example**

This example shows eight channels (or bits) on probe pod 1 mapped to two labels in the interface. Bits 0-3 are assigned to label Bus\_A, and bits 4-7 are assigned to label Bus\_B. When a bit is assigned, an asterisk "\*" appears in the bit assignment field, verifying the software connection.

#### Overview of the HP 16522A Pattern Generator

NOTE:

After you set up your first measurement, use the ribbon cable ID clips to mark the data cable numbers for future reference.

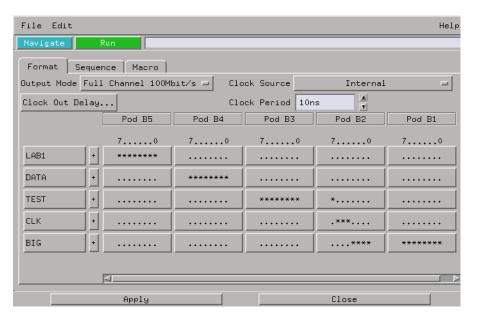

# Vector Output Mode

Output Mode Full Channel 100Mbit/s =

The Vector Output Mode determines the channel width, available pods, and the frequency range for both the internal and external clock. The choice you make may be determined by trade-offs between clock speed and channel width.

Because the output mode affects clock frequency ranges, available pods, and channel width, keep your mode selection in mind when designing the circuit's hardware interface and when mapping probe connections between the test circuit and the labels of the pattern generator.

This table shows the difference between the Full-Channel 100 MBits/s mode and the Half-Channel 200 MBits/s mode.

|                                     | Full Channel 100 MBits/s | Half Channel 200 MBits/s                     |

|-------------------------------------|--------------------------|----------------------------------------------|

| Pods Available                      | Pods 1, 2, 3, 4, 5       | Pods 1, 3, 5                                 |

| Maximum Channels                    | 40; eight per pod        | 20; eight on pods 1, 3, and lower 4 on pod 5 |

| Maximum External Clock<br>Frequency | 100 MHz                  | 200 MHz                                      |

| Maximum Internal Clock<br>Frequency | 100 MHz                  | 200 MHz                                      |

| Minimum External Clock<br>Frequency | DC                       | DC                                           |

| Minimum Internal Clock<br>Frequency | 4 kHz                    | 4 kHz                                        |

## **Clock Source**

The Clock Source field toggles between internal and external. The internal clock source is supplied by the pattern generator and controls the frequency used to output the vectors to the system under test. The external clock is provided by the user or the system under test, and is input to the pattern generator through the CLK IN probe of a clock pod.

An advantage of using an external clock is that you synchronize the vector output of the pattern generator to the system under test. No matter which clock source is used, vectors are always output on the rising edge of the clock.

#### Internal Clock Source

Use an internal clock source when you want to have control over the frequency of the output vectors and it is not important for the output vectors to be synchronized to the system under test.

You select clock periods in steps of 1, 2, 2.5, 4, 5, 8, and 10. If you use

#### Overview of the HP 16522A Pattern Generator

the keypad to select a value between the step intervals, the value is rounded to the nearest interval.

#### NOTE:

If you use the keypad to change the the clock period value, you must press the *Enter key* to register the new value.

The minimum clock period available with Vector Output Mode at Full Channel 100Mbit/s is 10 ns. The minimum clock period available with Vector Output Mode at Half Channel 200Mbit/s is 5 ns. Maximum clock period for either mode is 250 us.

#### **External Clock Source**

Use an external clock source when you want to synchronize the frequency of the output vectors to the system under test. With this mode selected, you do not have direct control over the frequency of the output vectors. Output vector frequency will be the same as the external clock.

When using an external clock source, be sure to set the clock period range to match the period of the external clock source. If the Vector Output Mode is Full Channel 100Mbit/s, you are offered two clock period ranges:

- Greater than or equal to 20 ns

- ullet Greater than or equal to 10 ns but less than 20 ns

If the Vector Output Mode is Half Channel 200 Mbit/s, you are offered three clock period ranges:

- Greater than or equal to 20 ns

- Greater than or equal to 10 ns but less than 20 ns

- Less than 10 ns

#### CAUTION:

If the external clock is faster than the period range selected, the HP 16522A will produce erroneous output vectors.

#### **Clock Out Delay**

Clock Out Delay...

The clock out delay setting lets you position the output clock with respect to the data. The zero setting is uncalibrated and should be measured to determine the initial position with respect to the data. Each numerical change of one on the counter results in an approximate change of 1.3 ns.

See Also

"Clock Circuit PGTheory" on page 93

# **Building a Sequence of Test Vectors**

Test vectors determine the pattern output at each clock cycle. Test vectors are positioned in a list called a sequence. When a sequence is run (see page 18), the list of vectors is executed in order of first vector to last vector. Vectors are always output on the rising edge of the clock.

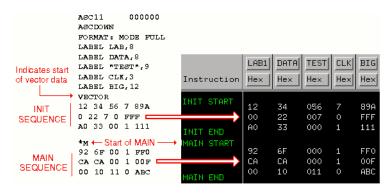

In every pattern generator application, you have two sequences. An INIT SEQUENCE (initialization sequence) is used to place your circuit or subsystem in a known state. The initialization sequence is followed by the MAIN SEQUENCE. The main sequence is used for the actual pattern generation that stimulates your circuit under test. The INIT sequence is only run once, while the MAIN sequence loops if you select a repetitive run.

### **Using Hardware and Software Instructions**

In addition to test vectors, both INIT and MAIN sequences can include predefined instruction (see page 56) elements. Instructions can create Breaks, Loops, Wait and If Events, and can even signal the Intermodule Bus. The most useful instruction is "*User Macro*". With a User Macro instruction, you can create reusable sequences that accept parameters. This flexibility is very useful in prototype turn-on and environmental testing.

For more information on INIT and MAIN sequences and how to create them, see the following topics.

#### Overview of the HP 16522A Pattern Generator

"Building an Initialization Sequence" on page 22

"Building a Main Sequence" on page 24

"Building a User Macro" on page 26

"Working with Instruction Types" on page 56

# Running the Pattern Generator

If you are not changing the run options, simply point to the *Group Run* field and click the *left mouse button* to run a measurement. To cancel a *Repetitive* run, click the *Cancel* field.

#### See Also

"Run/Group Run Function" on page 105

"What Happens when Run is Selected" on page 18

"What Happens when Stop is Selected" on page 18

# What Happens when Run is Selected

In single run mode, the vectors are output from the first vector in the initialization sequence to the last vector of the main sequence. The last vector of the main sequence will be held at the outputs until you run again.

In repetitive run mode, the vectors in the initialization sequence will be output from first to last, one time, then the main sequence will repetitively output the vectors in that sequence until you press the Stop field.

# What Happens when Stop is Selected

When the pattern generator acknowledges stop, the vector currently being output will be held at the outputs until you run again.

# A Beginner's Exercise

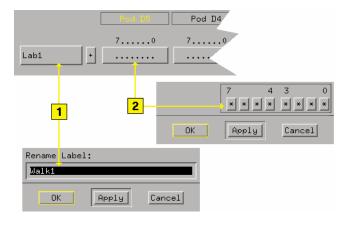

This exercise begins with the pattern generator Format tab active. If it is not active, click *Format* in the pattern generator window now.

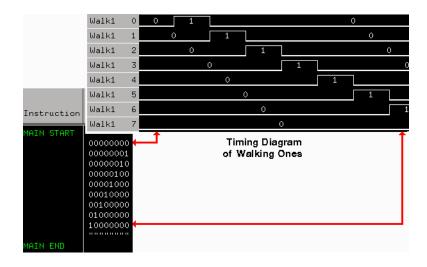

In this exercise, you will create a label with eight output channels assigned to it. You will then create a "Walking Ones" output pattern using one of the automatic pattern fill functions.

#### NOTE:

This exercise does NOT require you to connect the probes or view the output. The intent of this exercise is to give you practice configuring the pattern generator interface. A timing analyzer display of the results is furnished for you.

- 1. Configure Format (see page 19) with a label called "Walk1" and all eight bits of Pod 5 assigned.

- 2. Click Sequence.

- 3. Configure Sequence (see page 20) with a Walking Ones sequence.

- 4. View the results. (see page 21)

#### See Also

"Help - How to Navigate Quickly" on page 104

# **Configure Format**

- 1. In the pattern generator's Format area, left-click the label Lab1, then select Rename. In the Rename dialog, type "Walk1", then click OK.

- 2. Left-click the bit assignment field under Pod 5 and set all eight bits to "\*" (on) by clicking them, then click OK.

## A Beginner's Exercise

See Also

"Help - How to Navigate Quickly" on page 104

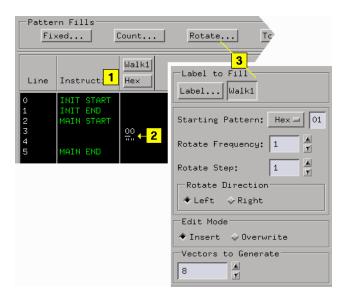

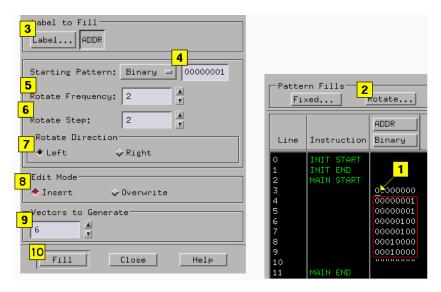

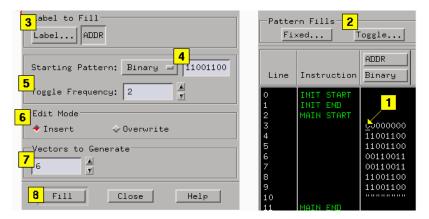

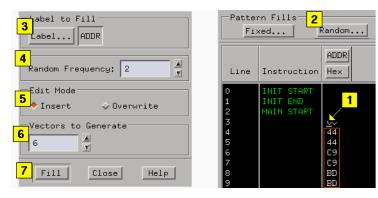

# Configure Sequence

- 1. In the pattern generator's Sequence area, right-click Hex and set the numeric base to Binary.

- $2. \;\;$  Left-click the first sequence line. This positions the cursor.

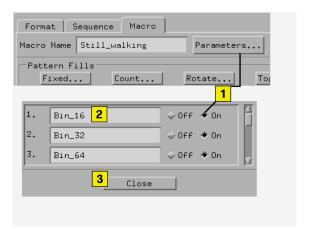

- 3. Left-click Rotate, and configure the Rotate Pattern Fill dialog as shown. Click Fill.

See Also

"Help - How to Navigate Quickly" on page 104

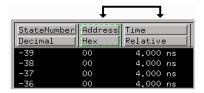

# View the Results

See Also

"Help - How to Navigate Quickly" on page 104

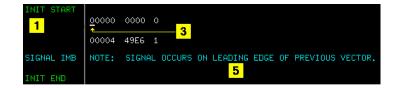

# **Building an Initialization Sequence**

The initialization (INIT) sequence is the first of two vector sequences that appear in the Sequence display. Use the INIT sequence to put the circuit or subsystem into a known starting condition. You can also use the INIT sequence to arm a logic analyzer or oscilloscope with the Signal IMB instruction to begin a measurement when the MAIN sequence begins. If you leave the INIT sequence empty, it will be ignored.

#### What Happens when Run is Selected

In single run mode, the vectors are output from the first vector in the initialization sequence to the last vector of the main sequence. The last vector of the main sequence will be held at the outputs until you execute run again.

In repetitive run mode, the vectors in the initialization sequence will be output from first to last, one time, then the main sequence will repetitively output the vectors in that sequence until you select *Stop*.

#### **Building the INIT Sequence**

The INIT sequence can contain hardware and software instructions (see page 56) as well as vector data. However, instructions are not allowed on the first two vector lines.

- 1. Click the Sequence tab, point to INIT START and left-click the mouse. This positions the cursor.

- 2. Press the Insert key on your keyboard one time for each new vector line you want to insert.

- 3. Point to the left-most character in the new vector line and left-click the mouse. This positions the cursor.

- 4. Type in the desired vector data. As you type, the default cursor wrap (see page 97) setting will roll the cursor left-to-right and top line to bottom line.

- 5. Optional If applicable, insert an instruction (see page 56) instead of typing vector data.

#### NOTE:

With the Vector Output Mode of *Half Channel 200 Mbit/s*, the INIT sequence must contain a number of vectors that is divisible by four. If this is not the case, the first vector of the INIT sequence is duplicated to create the correct number of vectors. With the Vector Output Mode of *Full Channel 100 Mbit/s* and vector frequencies greater than 50 MHz, the INIT sequence must contain an even number of vectors. Again, if this is not the case, the first vector of the INIT sequence is duplicated to create the correct number of vectors.

#### See Also

"Working with Labels and Pods" on page 66

"Editing Sequences" on page 50

"Working with Instruction Types" on page 56

"Building a User Macro" on page 26

"Automatic Cursor Wrap" on page 97

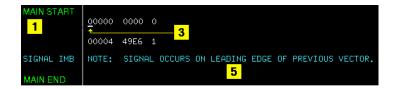

# Building a Main Sequence

The MAIN sequence is the second of two vector sequences that appear in Sequence. Use the MAIN sequence as the primary signal generation sequence. The MAIN sequence must contain at least two vectors to output.

#### What Happens when Run is Selected

In single run mode, the vectors are output from the first vector in the initialization sequence to the last vector of the main sequence. The last vector of the main sequence will be held at the outputs until you select run again.

In repetitive run mode, the vectors in the initialization sequence will be output from first to last, one time, then the main sequence will repetitively output the vectors in that sequence until you select the *Stop* field.

### **Building the Main Sequence**

The MAIN sequence can contain hardware and software instructions (see page 56) as well as vector data. However, instructions are not allowed on the first two vector lines or the last vector line.

- 1. *Click* the Sequence tab, *point* to MAIN START and left-click the mouse. This positions the cursor.

- 2. Press the Insert key on your keyboard one time for each new vector line you want to insert.

- 3. Point to the left-most character in the new vector line and left-click the mouse. This positions the cursor.

- 4. Type in the desired vector data. As you type, the default cursor wrap (see page 97) setting will roll the cursor left-to-right and top line to bottom line.

- 5. Optional If applicable, insert an instruction (see page 56) instead of a typing vector data.

#### See Also

- "Working with Labels and Pods" on page 66

- "Editing Sequences" on page 50

- "Working with Instruction Types" on page 56

- "Building a User Macro" on page 26

- "Automatic Cursor Wrap" on page 97

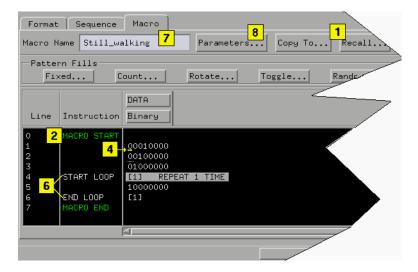

# Building a User Macro

A User Macro is a vector sequence defined by a custom name, then inserted by name into a sequence wherever the macro is needed. Macros may be inserted into the INIT or MAIN sequences of the vectors in Sequence, or into other macros. Using macros gives you the benefit of keeping INIT or MAIN sequences generic. By simply interchanging macros, you change the pattern generator output.

#### NOTE:

Care should be taken to avoid infinite loops. For example, if macro 0 calls macro 1, and macro 1 calls macro 0, this will cause an infinite loop.

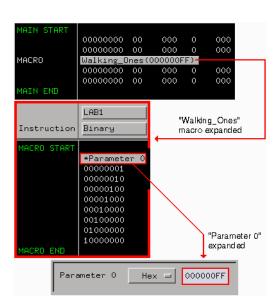

Macros can also accept parameters (see page 79). A major benefit in using parameters is that you keep a macro's functionality generic and still direct specific action identified by parameters. Think of a parameter as the only part of a macro that changes as the macro is reused. Each macro can accept a maximum of 10 unique parameters.

Typically, you create a macro first under the *Macro* tab, then insert it into sequences under the *Sequence* tab. You can create 100 different macros for use in one or more pattern generator sequences.

Differences between User Macros and the INIT and MAIN sequences are that macros cannot use the "If" instruction or any instruction that interacts with the intermodule bus (IMB). The reason is that these instructions can only be included once into the sequence. Since macros may be called as many times as desired, allowing these instructions within macros would violate this restriction. You remove macros from sequences by using the  $Delete\ Line(s)$  function.

## **Creating the Macro**

A macro sequence can contain hardware and software instructions (see page 56) as well as vector data. However, instructions are not allowed on the first vector line.

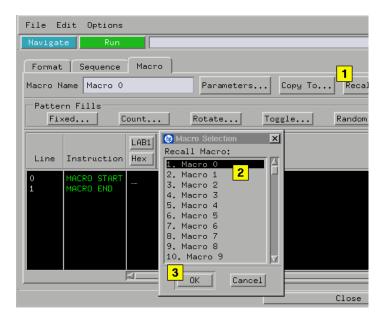

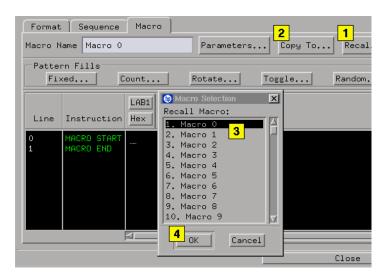

- 1. In Macro, recall (see page 98) the macro that you want to create.

- 2. *Point* to MACRO START and left-click the mouse. This positions the cursor.

- 3. Press the Insert key on your keyboard one time for each new vector line you want to insert.

- 4. Point to the left-most character in the new vector line and left-click the mouse. This positions the cursor.

- 5. Type in the desired vector data. As you type, the default cursor wrap (see page 97) setting will roll the cursor left-to-right and top line to bottom line.

- Optional Insert an instruction (see page 56) instead of a typing vector data.

- 7. Type in a name for the new macro.

- 8. Optional Click *Parameters* and turn on any parameters you plan to use.

### Inserting the Macro

- 1. In *Sequence* or *Macro*, point to the vector line directly above where you want to insert the User Macro instruction.

- 2. Press and hold the right mouse button while pointing to *Insert After*. Release the right mouse button.

- 3. Point to the User Macro instruction and right-click.

- 4. From the Macro Selection dialog that appears, left-click the desired macro name you want to insert.

## **Building a User Macro**

5. Click OK.

## NOTE:

See The User Macro Instruction (see page 63) for restrictions on User Macro instruction usage.

## See Also

"Recalling Macros" on page 98

"Copying Macros" on page 100

"Working with Macro Parameters" on page 79

"Working with Instruction Types" on page 56

"Editing Sequences" on page 50

"Working with Labels and Pods" on page 66

# Importing HP 16522A ASCII Files

You can create an ASCII text file and import it into as a complete pattern generator program. In general, the ASCII file consists of a block of setup information, a block of label and channel information, and a block of pattern generator vector data. The file must be saved in ASCII format and organized as shown in step 1 of the procedure below.

- 1. Create the ASCII file (see page 31) in a text editor.

- 2. Save the file as *Text Only* or *ASCII Format* in a directory on your analyzer's hard drive.

- 3. In Sequence's menu bar, select *File*, then *Import 16522A ASCII File*. See the caution below.

- From the file selection dialog that appears, select the desired path and ASCII file name.

- 5. Click Import.

#### **CAUTION:**

Importing an HP 16522A ASCII file causes all current Format and Sequence information to be overwritten. Be sure to save the pattern generator configuration before you begin the import process.

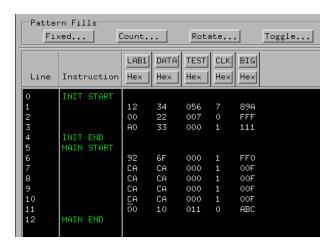

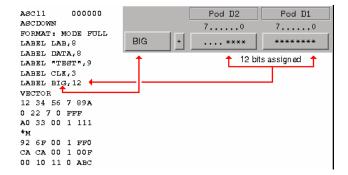

This figure shows Sequence after the ASCII file example shown in step 1 was imported.

## **Importing HP 16522A ASCII Files**

This figure shows Format after the ASCII file example shown in step 1 was imported.

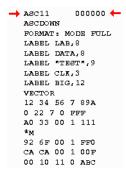

# Creating an ASCII File

You can create an ASCII file using any MS-DOS or UNIX text editor. An ASCII file consists of a file identifier and three blocks of information. Each block must follow the specified order.

ASCII 000000 - required file identifier ("ASCII" followed by 5 spaces and 6 zeros).

ASCDown - optional. Retained for backwards compatibility.

• 1st block (optional)

FORMat - clock, channel mode, and delay information.

• 2nd block

LABel - names and number of channels.

3rd block

VECTor - vector data and Repeat indicators.

#### **File Requirements and Precautions**

- The file must contain only specified pattern generator commands (see page 33), and in the order and format shown in the example below.

- The file must be saved in "ASCII" or "text only" format.

- Vector data is assumed to be entirely hexadecimal base.

- No pattern generator instructions are allowed in the data.

- No pattern generator macros are defined or invoked in the data.

- All labels consist of adjacent bits.

- The file must end with a line termination character (line feed "<lf>" or a carriage return and line feed "<CR><lf>".

- Comments can be included after the first line (ASCII 000000). Comments begin with a slash '/' and terminate at the end of the line.

#### **Importing HP 16522A ASCII Files**

#### **ASCII File Example**

#### NOTE:

In this example, the underlined links are added for documentation purposes only, and would NOT be part of an actual disk file's text. Line feeds "<lf>" are shown for example purposes only, and depending on the computer and text editor used, could actually be a carriage return followed by a line feed "<CR><lf>".

```

ASCII 000000 (see page 33)<lf>

/ This is a test of the ascii file

ASCDown (see page 34)<lf>

FORMat: MODE FULL (see page 37)<lf>

FORMat: CLOCk INTernal, 10E-9 (see page 37)<lf>

LABel LAB1, 8 (see page 34)<lf>

LABel DATA, 8<lf>

LABel TEST, 9<lf>

LABel CLK, 3<lf>

LABel BIG, 12<lf>

/* This is the beginning of the vector part

/*

VECTor (see page 35)<lf>

12 34 056 7 89A<lf>

/ Some vectors

0 22 007 0 FFF<lf>

/* Some more vectors */

A0 33 000 1 111<lf>

M<lf>

92 6F 000 1 FF0<lf>

CA CA 000 1 00F<lf>

// Even more vectors

*R 3<lf>

00 10 011 0 ABC<lf>

```

#### NOTE:

The LABel sequence specified in the 8th through 12th lines results in a specific bit assignment. A different ordering of the LABel commands would give a different ordering to the bits.

### **ASCII Disk File Identifier**

The first line of a disk file must contain the text string "ASCII 000000". It consists of the text "ASCII" followed by 5 blanks, then 6 zeros. The purpose of this string is to uniquely identify the file as an ASCII disk file.

#### Example

# **ASCII File Commands**

The following commands are used in the ASCII file to configure Sequence and Format. Commands are not case sensitive. Lowercase letters in an illustrated command simply show the long and short form difference.

The uppercase letters of the command show the mandatory portions of each command.

#### **Commands**

```

"ASCDown Command" on page 34

FORMat Commands

MODe (see page 37)

CLOCk (see page 37)

```

#### **Importing HP 16522A ASCII Files**

DELay (see page 38)

"LABel Command" on page 34

"VECTor Command" on page 35

### **ASCDown Command**

The ASCDown command was formerly used to signal the start of an ASCII file load. It causes the current pattern generator label and sequence structures to be cleared and reset to a default state. The HP 16522A pattern generator now does this automatically.

#### **Example**

```

ASC11

000000

📤 ascdown 🛑

FORMAT: MODE FULL

LABEL LAB,8

LABEL DATA, 8

LABEL "TEST",9

LABEL CLK, 3

LABEL BIG, 12

VECTOR

12 34 56 7 89A

0 22 7 0 FFF

AO 33 OO 1 111

*M

92 6F 00 1 FF0

CA CA 00 1 00F

00 10 11 0 ABC

```

#### **LABel Command**

The LABel command is a special means of specifying labels for use by an ASCII file. The label bits are assigned from most to least significant bits across the output pods. You must specify the label string (quotation marks on the string are optional) and the width of the field. The label base defaults to hexadecimal. There are a maximum of 126 labels. No label may be more than 32 bits wide. If a label is too wide (too many bits) for the remaining unused pattern generator bits, it will be discarded.

#### **Command Syntax**

```

LABel <name_str>, <width> <name_str> = label string a maximum of 20 characters in length. <width> = integer number of bits in the label (1 through 32).

```

#### **Example**

#### **VECTor Command**

The VECTor command is used after the end of the header/setup commands to signal the start of the actual pattern generator data in an ASCII file. No data is allowed in the same line as the VECTor command.

#### **Example**

#### **Vector Data**

The data portion of the ASCII file is an array of hexadecimal data fields. Each row of the array corresponds to a single line of the main program. Each column of the array corresponds to a single label as defined under the pattern generator Format tab.

Data fields are separated by one or more blank characters. A line termination (line feed or carriage return + line feed) signals the end of

## **Importing HP 16522A ASCII Files**

a line and the start of a new line. If a data field has more data than the label width would indicate, only the least significant bits of the data field are used. If there are more data fields in a row than there are labels, the extra data fields (last data fields in the row) are ignored. If there are fewer data fields in a row than there are labels, the data for the extra (right-most) labels will be zero.

The MAIN sequence must have at least two data lines. In the ASCII data file, a row consisting of only "\*M" signals the start of the MAIN sequence. If there is to be no data in the INIT sequence, the first row of the file after the VECTor command must be "\*M". Note that the quotation marks in "\*M" are not really in the file.

#### CAUTION:

Any character that is not a valid hexadecimal digit (that is, 0 through 9, or upper/lower case A through F) are ignored and treated as field separators. This could cause problems if a mistyped character appears in the middle of a data value. For example, "12R4" will be assigned to two labels as "12" and "4".

Either of the INIT or MAIN sequences can include multiple Repeat indicators specified by "\*R <count>". Note that the quotation marks around the Repeat indicator are not part of the indicator, and like the "\*M", the "\*R <count>" must be located on a separate line.

The Repeat indicator specifies that the previous data vector is repeated <count> more times, where <count> is a positive integer. The Repeat indicator must follow a sequence line containing a data vector or another Repeat indicator. Placing the Repeat indicator after the VECTor command or the "\*M" will cause an error message to appear.

The last data row of the file must end with a line termination character. The line termination character is the flag to load the data row into the data structure. Failure to do this will result in the last data row not being loaded.

The ASCII file import mechanism assumes correctness in the data file and any header commands. Error handling is basic, and treating unexpected characters as field separators could create bizarre results when parsing the file. Error messages point to the line number where the parser finds the error.

Serious problems will cause the default main program to be loaded in an effort to avoid locking up the logic analysis system.

## FORMat:MODe Command

The FORMat:MODe command is optional. The existing mode scheme is used if nothing is specified. FULL channel output mode limits the data rate to a maximum of 100 MHz, but allows 40 channels per card. HALF channel output mode allows an output rate of greater than 100 MHz, but limits the number of channels to 20 per card.

## **Command Syntax**

FORMat: MODe [FULL | HALF]

## **Example**

```

000000

ASC11

ASCDOWN

FORMAT: MODE FULL -

LABEL LAB, 8

LABEL DATA, 8

LABEL "TEST",9

LABEL CLK, 3

LABEL BIG, 12

VECTOR

12 34 56 7 89A

0 22 7 0 FFF

AO 33 00 1 111

92 6F 00 1 FF0

CA CA 00 1 00F

00 10 11 0 ABC

```

## FORMat:CLOCk Command

The FORMat:CLOCk command is optional. The existing clock scheme is used if nothing is specified. The CLOCk command specifies the clock source for the pattern generator.

## **Command Syntax**

```

FORMat:CLOCk INTernal, <clk_period> = a real number value that corresponds to the interface selectable clock period values (example = 5E-9).

```

```

FORMat:CLOCk EXTernal, [LEFifty|GTFifty|GTONe] [LEFifty] = Less than or equal to 50 MHz. [GTFifty] = Greater than 50 MHz and less than or equal to 100 MHz. [GTONe] = Greater than 100 MHz.

```

## **Importing HP 16522A ASCII Files**

NOTE:

The maximum clock rate is limited by the channel mode. See FORMat:MODe (see page 37) command.

## **Example**

```

ASC11

000000

ASCDOWN

FORMAT: MODE FULL

FORMAT: CLOCK INTERNAL, 10E-9 🛑

LABEL LAB, 8

LABEL DATA, 8

LABEL "TEST",9

LABEL CLK, 3

LABEL BIG, 12

VECTOR

12 34 56 7 89A

0 22 7 0 FFF

AO 33 00 1 111

*м

92 6F 00 1 FF0

CA CA 00 1 00F

00 10 11 0 ABC

```

## **FORMat:DELay Command**

The FORMat:DELay command is optional. The existing delay scheme is used if nothing is specified. The DELay command specifies the clock out delay. The clock out delay setting allows positioning of the clock with respect to the data. Delay setting range is 0 - 9 with each increment delaying the clock approximately 1.3 ns per step.

NOTE:

The delay setting that corresponds to zero is uncalibrated. You must measure it to determine the basic clock/data timing.

## **Command Syntax**

```

FORMat:DELay <delay_arg> <delay_arg> = an integer from 0 to 9 with each increment delaying the clock by approximately 1.3 ns.

```

## Example

```

ASC11

000000

ASCDOWN

FORMAT: MODE FULL

FORMAT: CLOCK INTERNAL, 10E-9

→ FORMAT: DELAY 2 ←

LABEL LAB,8

LABEL DATA, 8

LABEL "TEST",9

LABEL CLK,3

LABEL BIG, 12

VECTOR

12 34 56 7 89A

0 22 7 0 FFF

A0 33 00 1 111

*M

92 6F 00 1 FF0

CA CA 00 1 00F

00 10 11 0 ABC

```

# Importing System Data Files

If you store logic analyzer data using the File Out tool, in either Internal, ASCII, or Fast Binary format, you can import these files into the pattern generator's INIT or MAIN sequences.

The "Import System Data File" dialog will only load files saved using the File Out tool. For ASCII files created in a PC or UNIX text editor, use Import 16522A ASCII File (see page 29).

## **CAUTION:**

Importing a  $File\ Out$  tool file causes all current Format and Sequence information to be overwritten. Be sure to save the pattern generator configuration before you begin the import process.

- 1. *Click* the Sequence tab.

- 2. Select File from the menu bar, then Import System Data File.

- 3. From the Import System Data File dialog, load the desired File Out tool file. See the note below.

- 4. Select the desired data set (see page 41).

- 5. Select the desired labels (see page 41).

- 6. Select a data set range (see page 42) to import. If you select "Partial", the range integers you specify will correspond to state numbers found in a state listing of the same data set.

- 7. Select the location to insert the samples. Samples are inserted at the beginning of the selected sequence. See the caution below.

- 8. Click Import.

NOTE:

If in step 3 you typed the file name into the text entry field, you must press the Return key on your keyboard to start the file import process instead of clicking the *Import* field.

## **Data Sets**

A data set is defined as data captured from a single source. For example, the data captured from machine one of a logic analyzer is a single source. Because the File Out tool allows multiple machines worth of data to be stored within the same file, you pick only one data set to import into the pattern generator.

## **Data Set Labels**

All labels in a single data set are listed along with each label's corresponding channel width. If a label is wider than the pattern

## **Importing System Data Files**

generator's maximum allowable channel width (32 channels), the label is marked "unavailable". Labels wider than 32 channels cannot be selected.

## Data Set Range

When you select a data set, the "from" and "to" fields update to the minimum and maximum values of the state listing. Both positive and negative integers are valid.

## **CAUTION:**

If the range of data samples is too large for the pattern generator sequence (258048 vectors), a message will appear giving you the choice to continue or not. If you continue, data will be imported starting from the beginning of the file. At the point where you run out of vectors, data will be missing. To solve this problem, reduce the range of samples you are importing.

# Loading and Saving Pattern Generator Configurations

You can save pattern generator settings and data to a configuration file. You can also save any tools connected to the pattern generator. Later, you can restore your data and settings by loading the configuration file.

- Loading Configuration Files (see the *HP 16600A/16700A Logic Analysis System* help volume)

- Saving Configuration Files (see the *HP 16600A/16700A Logic Analysis System* help volume)

# Selecting the Correct Probe Pod

The following equivalent circuit information is provided to help you select the appropriate clock and data pods for your application.

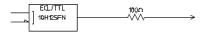

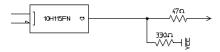

#### HP 10461A TTL Data Pod

Output type 10H125 with 100 ohm in series 200 MHz

Maximum clock

Typical less than 2 ns; worst case 4 ns (note 1)

Recommended lead set HP 10474A

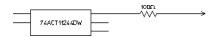

### HP 10462A 3-State TTL/CMOS Data Pod

Output type 74ACT11244 with 100 ohm in series

10H125 on non 3-state channel 7 (note 2), negative true, 100K ohm to GND, enabled 3-state enable

on no connect.

Maximum clock 100 MHz

Typical less than 4 ns; worst case 12 ns (note 1)

Recommended lead set HP 10474A

### **HP 10464A ECL Data Pod (terminated)**

10H115 with 330 ohm pulldown, 47 ohm in series Output type Maximum clock 200 MHz

Typical less than 1 ns; worst case 2 ns (note 1)

Recommended lead set HP 10474A

### **HP 10465A ECL Data Pod (unterminated)**

10H115 (no termination) Output type

Maximum clock 200 MHz

Skew Typical less than 1 ns; worst case 2 ns (note 1) Recommended lead set HP 10347A

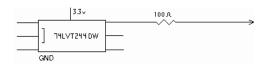

#### HP 10466A 3-State TTL/3.3 volt Data Pod

Output type 74LVT244 with 100 ohm in series 10H125 on non 3-state channel 7 (see note 2)

3-state enable 10H125 on non 3-state channel 7 (see note 2) negative true, 100K ohm to GND, enabled on no

connect.

Maximum clock 200 MHz

Skew Typical less than 3 ns; worst case 7 ns (note 1)

Recommended lead set HP 10474A

#### Note 1

Typical skew measurements made at the pod connector with approximately  $10~\mathrm{pF/50K}$  ohm load to GND; worst case skew numbers are a calculation of worst case conditions through circuits. Both numbers apply to any channel within a single or multiple module system.

#### Note 2

Channel 7 on the 3-state pods has been brought out in parallel as a non 3-state signal. By looping this output back into the 3-state enable line, the channel can be used as a 3-state enable.

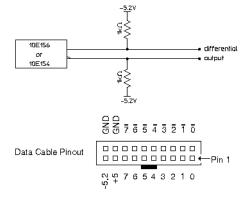

#### **Data Cable Characteristics without a Data Pod**

The HP 16522A data cables without a data pod provide an ECL-terminated (1K ohm; to -5.2V) differential signal. These signals are usable when received by a differential receiver, preferably with a 100

ohm termination across the lines. These signals should not be used single-ended due to the slow fall time and shifted voltage threshold; they are not ECL compatible.

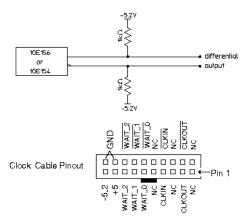

#### **Clock Cable Characteristics without a Clock Pod**

The clock out signals (CLKOUT and not-CLKOUT) without a clock pod provide an ECL-terminated (1K ohm to -5.2V) differential signal. These signals are usable when received by a differential receiver, preferably with a 100 ohm termination across the lines. These signals should not be used single-ended due to the slow fall time and shifted voltage threshold; they are not ECL compatible.

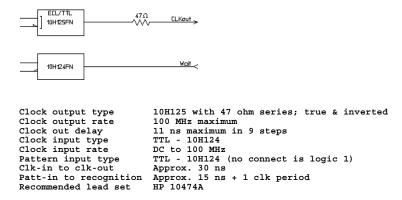

### 10460A TTL Clock Pod

## 10463A ECL Clock Pod

Clock output type 10H116 differential unterminated; differential with 330 ohm to -5.2v and 47 ohm series

Clock output rate 200 MHz maximum

Clock input type ECL - 10H116 with 50K ohm to -5.2v

Clock input rate DC to 200 MHz

Pattern input type ECL - 10H116 with 50K ohm (no connect is logic 0)

Clk-in to clk-out Approx. 30 ns

Patt-in to recognition Approx. 15 ns + 1 clk period

Recommended lead set HP 10474A

See Also

"Connecting the Probe Pods" on page 48

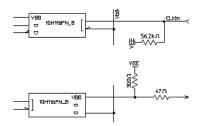

## **Connecting the Probe Pods**

# Connecting the Probe Pods

NOTE:

Clock and Data pods are required for a proper signal interface. (see page 94) There are different types (see page 44) available, and they should match your target circuit characteristics. In addition, depending on the Vector Output Mode (see page 14) selected, some pods may not be available for use.

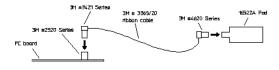

## **Direct Pod-to-Board Connection**

Plug the pod directly into the ©3M 2520-series, or similar alternative connector on the PC board.

## **Jumper Cable-to-Pod Connection**

Use this method when you have clearance problems on the PC board. Construct a flat-ribbon cable and connect as shown above.

NOTE:

You can obtain equivalent connectors from sources other than 3M.

## **Probe Lead Set to Board Pin Connection**

Two probe lead assemblies are available for connecting to PC board pins.

- HP 10474A 8-channel probe lead set.

- HP 10347A 8-channel probe lead set, 50-ohm coaxial for unterminated signals.

The probe tips of both lead sets plug directly into any 0.1-inch grid with 0.026- to 0.033-inch diameter round pins or 0.025-inch square pins. These probe tips work with the HP 5090-4356 surface mount grabbers and the HP 5959-0288 through-hole grabbers.

# **Editing Sequences**

- "Cutting, Copying, Pasting, and Deleting Sequence Lines" on page 50

- "Deleting Sequence Lines" on page 51

- "Inserting Blank Sequence Lines" on page 53

- "Go to a Line Number" on page 53

- "Positioning the Sequence" on page 54

- "Using Ditto " values" on page 54

# Cutting, Copying, Pasting, and Deleting Sequence Lines

#### NOTE:

When you use the *Cut* and *Copy* operations from the menu bar, you are placing the sequence lines in a temporary storage buffer. All subsequent *Paste* operations will insert sequence lines from the storage buffer until new lines are cut or copied. When you use the *Delete* operation from the menu bar, the sequence lines are not placed in the temporary buffer. They are just deleted.

- Select the sequence lines to cut, copy, or delete by pointing to the first line.

- 2. Press and hold the left mouse button while dragging the cursor either up or down. To select the entire sequence, select *Edit* from the menu bar, then *Select All Lines*.

- 3. From the menu bar, select *Edit*, then *Cut Line(s)*, *Copy Line(s)*, or *Delete Lines(s)*.

- 4. Left-click the sequence line just above where you want to paste the sequence lines. This positions the cursor. When pasting sequence lines, the lines are placed *after* the cursor line.

- 5. If you are pasting cut or copied lines, select *Edit* from the menu bar, then *Paste Line(s)*.

### NOTE:

Cutting or deleting all the sequence lines causes the sequence to be reset to the power-up state.

#### **Restrictions on Use**

The above operations will not be allowed if the result of the operation places an instruction on one of the following vectors:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

In addition, the above operations will not be allowed if the result of the operation places a hardware instruction immediately after another instruction. Hardware instructions must follow data vectors.

## **Deleting Sequence Lines**

## **CAUTION:**

When you delete sequence lines using the keyboard, they are permanently removed. If you want to place them in a temporary storage buffer, use the Cut (see page 50) operation from the menu bar.

## **Deleting Single Lines**

- To delete single lines, left-click anywhere on the line to position the cursor, then press the *Delete* key on the keyboard.

- To delete multiple lines, select the lines to delete by pointing to the first line, then press and hold the left mouse button while dragging the cursor either up or down. Then press the *Delete* key on the keyboard.

### **Editing Sequences**

#### **Delete All Lines**

To delete all lines in a sequence, go to the menu bar and select  $Edit -> Select All \ Lines$ , then  $Edit -> Delete \ Lines(s)$ . Deleting all lines causes the sequence to be reset to the power-up state.

### **Restrictions on Use**

You are not allowed to delete the following sequence lines:

- The INIT START line.

- The INIT END line.

- The MAIN START line.

- The MAIN END line.

- The MACRO START line.

- The MACRO END line.

A delete will not be performed if the result of the delete places an instruction on one of the following lines:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

A delete will not be performed if the result of the delete does either of the following:

- Places a hardware instruction immediately after another instruction.

- Causes the MAIN sequence to contain fewer than two data vectors.

## **Inserting Blank Sequence Lines**

Use the Insert key on the keyboard to insert blank lines (see page 54) below the cursor. This is a very useful operation when starting a new sequence. After you insert a new line, you replace the ditto values with the desired normal data values.

### NOTE:

The new blank lines are inserted with ditto values.

- 1. *Point* to the vector line directly above where you want to insert lines and left-click the mouse. This positions the cursor.

- 2. Press the Insert key on your keyboard one time for each new vector line you want to insert.

### NOTE:

The "I" key on the keyboard works the same way as the *Insert* key on the keyboard.

In addition, you can insert blank sequence lines by using the mouse as follows:

- 1. Point to the vector line directly above where you want to insert the new data vector.

- 2. Press and hold the right mouse button, point to *Insert After*, then select *Vector*.

#### See Also

"Using Ditto " values" on page 54

## Go to a Line Number

- 1. From within the *Sequence* or *Macro* tab, *point* to any vector line.

- 2. Press and hold the right mouse button, then select *Goto Line*.

- 3. In the Goto Line dialog that appears, enter the desired line number.

- 4. Click OK.

### **Editing Sequences**

#### See Also

"Positioning the Sequence" on page 54

# Positioning the Sequence

Among the keyboard keys that insert and delete data vectors, the pattern generator defines four other keys used to position the sequence when either the *Sequence* or *Macro* tab is active. Specifically, these additional keys are defined:

- 1. Home move to the first line of the sequence.

- 2. End move to the last line of the sequence.

- 3. Page Up scroll upward by one screen's worth of data.

- 4. Page Down scroll downward by one screen's worth of data.

To use the positioning keys, perform the following steps:

- 1. From within Sequence or Macro, *point* to any vector line.

- 2. Press one of the above keys on the keyboard.

#### See Also

"Go to a Line Number" on page 53

## Using Ditto "values

In any existing data vector, with the exception of the first, you can replace normal data values with ditto values (designated by the double quotation marks).

Ditto values indicate that the previous data value should be repeated for the current data vector. Ditto values save you effort by requiring you to only type in the data values that change.

NOTE:

When you insert blank lines, they are inserted as ditto values.

- 1. From either the *Sequence* or *Macro* tab, left-click the *data field* that you want to edit. This positions the cursor.

- 2. Type in the ditto values using the double quotation mark key on the keyboard.

## NOTE:

Ditto characters following an IF block always evaluate to the last vector in the IF block regardless of whether the block is executed or not.

## See Also

"Inserting Blank Sequence Lines" on page 53

# Working with Instruction Types

Instructions are like programming commands. They are inserted into a sequence for the purpose of executing their designated control over the flow of the sequence. There are two types of instructions: hardware and software. The differences between these types are described below.

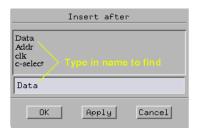

## **Inserting Instructions into Sequences**

- 1. *Point* to the vector line directly above where you want to insert the new instruction.

- 2. Press and hold the right mouse button while pointing to *Insert After*. Then release the button.

- 3. *Right-click* the desired instruction to insert.

## **Hardware Instruction Types**

The following hardware instruction types are available. Each of these instructions can affect external hardware or the pattern generator hardware.

- "The Break Instruction" on page 57

- "The Signal IMB Instruction" on page 58

- "The Wait IMB Event Instruction" on page 58

- "The Wait External Event Instruction" on page 59

- $\bullet\,\,\,$  "The If External Event Instruction" on page  $60\,\,$

- "The If IMB Event Instruction" on page 61

## **Software Instruction Types**

The following software instruction types are available. Each of these instructions only affects the execution flow of the currently running

sequence. However, a User Macro software instruction can include hardware instructions.

- "The User Macro Instruction" on page 63

- "The Repeat Loop Instruction" on page 64

#### See Also

- "Building a Main Sequence" on page 24

- "Building an Initialization Sequence" on page 22

- "Building a User Macro" on page 26

## The Break Instruction

The Break instruction causes a break at the current vector. In single run mode, this instruction halts the sequence and holds the outputs at the value of the previously outputted data value. In repetitive run mode, this instruction pauses the sequence at the current vector momentarily, then continues. The duration of the pause depends on the activity of other modules in the frame.

#### **Restrictions on Use**

The Break instruction must follow data vectors. Also, the Break instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

## The Signal IMB Instruction

The Signal IMB instruction creates an arming signal on the *intermodule bus* when the instruction is executed. This *arming* signal allows the pattern generator to *cross trigger* other modules in the frame.

#### **Restrictions on Use**

The Signal IMB instruction, as with all hardware instructions, must follow data vectors. Also, the Signal IMB instruction can only be used one time in a sequence, and consequently it is not allowed in a user macro or a repeat loop. The Signal IMB instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

See Also

Using the Intermodule Window (see the HP 16600A/16700A Logic Analysis System help volume)

## The Wait IMB Event Instruction

The Wait IMB Event instruction halts the execution of the program sequence until an IMB signal is received by the pattern generator.

#### **Restrictions on Use**

The Wait IMB Event instruction, as with all hardware instructions, must follow data vectors. Also, the Wait IMB Event instruction can only

be used one time in a sequence, and consequently it is not allowed in a user macro or a repeat loop. The Wait IMB Event instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

## The Wait External Event Instruction

The Wait External Event instruction halts the execution of the program sequence until one of four designated events (A-D) is received by the pattern generator.

Because the Wait External Event is an OR'ing function of the toggled "On" wait patterns, as soon as one of the selected wait patterns is satisfied, the sequence continues. The wait patterns are specified on the three input lines of the clock pod: Wait0, Wait1, and Wait2.

To choose and configure a particular event, right-click the Wait External Event instruction, then from the External Wait Pattern dialog, toggle the appropriate fields.

### **Restrictions on Use**

The Wait External Event instruction, as with all hardware instructions, must follow data vectors. Wait External Events are not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

## **Working with Instruction Types**

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

## The If External Event Instruction

## NOTE:

The If External Event instruction is only available in Full Channel 100 Mbit/s mode with clock frequencies of 50 MHz and lower (or clock periods of 20 ns or longer).

The If External Event is an OR'ing function of the toggled "On" wait patterns. If one of the selected patterns is satisfied when the If External Event is evaluated, the If block is output. Otherwise, the If block is skipped.

The If External Event instruction uses the same three clock pod input lines (Wait0, Wait1, and Wait2) as the Wait External Event instruction. Right-click the instruction to bring up a dialog used to designate a three-bit data pattern for the pattern generator to compare against. Use the toggle buttons within the External If Pattern dialog to configure the "If" event.

The If External Event instruction inserts the following set of vector lines:

```

blank data vector

IF EXTERNAL

blank data vector

blank data vector

END IF

blank data vector

blank data vector

```

### NOTE:

Ditto characters following an IF block always evaluate to the last vector in the IF block regardless of whether it is executed or not.

The default data vectors inserted with the instruction are restricted.

They can contain vector data, but not instructions. Any new instructions inserted into an If External Event must obey the restrictions listed below. The "If Event" can be removed by deleting either the start or end of the If block.

#### NOTF:

With an If Event instruction (External or IMB) in a sequence, repetitive runs may have latency between the last and the first vectors of the MAIN SEQUENCE. This latency depends on the activity of other measurement modules in the frame, thus varying from run to run.

#### Restrictions on Use

The If External Event instruction, as with all hardware instructions, must follow data vectors. Also, the If External Event instruction can only be used one time in a sequence, and consequently it is not allowed in a user macro or a repeat loop. The If External Event instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

## The If IMB Event Instruction

#### NOTE:

The If IMB Event instruction is only available in Full Channel 100 Mbit/s mode with clock frequencies of 50 MHz and lower (clock periods of 20 ns or longer).

If an IMB signal is present when the If IMB Event instruction is executed, the data in the If block is output, otherwise it is skipped.

The If IMB Event instruction inserts the following set of vector lines:

blank data vector

IF IMB blank data vector

blank data vector

END IF blank data vector

blank data vector

### **Working with Instruction Types**

## NOTE:

Ditto characters following an IF block always evaluate to the last vector in the IF block regardless of whether it is executed or not.

The default data vectors inserted with the instruction are restricted. They can contain vector data, but not instructions. Any new instructions inserted into an If IMB Event must obey the restrictions listed below. Remove the If IMB Event by deleting either the start or end of the If block.

## NOTE:

With an If Event instruction (External or IMB) in a sequence, repetitive runs may have latency between the last and the first vectors of the MAIN SEQUENCE. This latency is dependent on the activity of other measurement modules in the frame, thus varying from run to run.

### **Restrictions on Use**

The If IMB Event instruction, as with all hardware instructions, must follow data vectors. Also, the If IMB Event instruction can only be used one time in a sequence, and consequently it is not allowed in a user macro or a repeat loop. The If IMB Event instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

## The User Macro Instruction

The User Macro instruction lets you insert a group of vectors that have a specific function. At run time, the user macro is expanded into its corresponding vectors. A typical macro application would be a generic test stimulus that is used by multiple circuits. By containing the device or circuit specific test vectors within a macro, you can simply interchange the macro and reuse the same INIT and MAIN SEQUENCE.

Macros can contain parameters. Using parameters in a macro gives you the same benefit as using macros in a sequence. By passing parameters, you can reuse the same macro for other purposes.

### **Restrictions on Use**

The User Macro instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

## **Working with Instruction Types**

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

#### See Also

"Building a User Macro" on page 26

"Working with Macro Parameters" on page 79

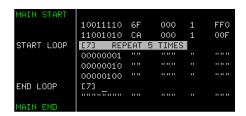

## The Repeat Loop Instruction

The Repeat Loop instruction inserts the start and end vectors of a repeat loop, along with one blank data vector row, below the selected vector row. Once the loop has been created, you can insert or copy vectors and instructions into the loop.

Set the number of loop repetitions (maximum 20,000) by right-clicking the "Start Loop" vector line and editing the  $Loop\ Count$  dialog. At run time, the loop count determines the number of times to expand the loop's body into individual vectors. Both the start and end vectors of a repeat loop are removed from the sequence if either one is included in a delete operation.

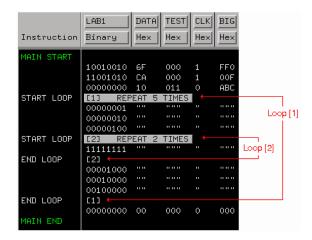

## **Nested Repeat Loop Instructions**

This example shows a nested loop. Loop[1] is a walking ones pattern that is repeated five times. Loop[2] is a bit pattern of all ones that is repeated twice directly in the middle of the walking ones pattern of Loop[1].

#### **Restrictions on Use**

The following instructions can NOT be used in a repeat loop:

- The Signal IMB instruction.

- The If External Event instruction.

- The If IMB Event instruction.

- The Wait IMB Event instruction.

The Repeat Loop instruction is not allowed on the following vector lines of a sequence:

- The first or second vector of the INIT sequence.

- The first or second vector of the MAIN sequence.

- The last vector of the MAIN sequence.

- The vector prior to the IF block.

- The first or second vector of the IF block.

- The last vector of the IF block.

- The first or second vector following the IF block.

# Working with Labels and Pods

Access label and pod operations from either the *Edit* pick in the menu bar, or under the label name field itself. When you select operations from the menu bar, they are global to all labels or pods in the window. When you select operations from under the label name, they are directed at the individual label.

In addition, label and pod operations in the *Sequence* and *Macro* displays are centered around adding or deleting. Operations in the *Format* display are centered around initial creation and configuration.

NOTE:

Label operations are performed on labels assigned in Format. If labels are not created, assigned bits, and turned on in Format, they do not appear in Sequence or Macro. Also, depending on the Vector Output Mode (see page 14), some pods may not be available.

## **Operations in Format**

- "Creating and Inserting New Labels" on page 67

- "Deleting Labels" on page 68

- "Renaming Existing Labels" on page 69

- "Reordering a Label's Pod Bits" on page 70

- "Turning Labels On/Off" on page 70

- "Clearing Format Labels" on page 71

- "Finding a label" on page 73

- "Swap Pods" on page 71

- "Clear Pods" on page 72

- "Assigning Bits to a Label" on page 72

- "Label Polarity" on page 73

## **Operations in Sequence and Macro**

• "Inserting Pre-assigned Labels" on page 69

- "Deleting Labels" on page 68

- "Replace Labels" on page 75

- "Finding a label" on page 73

- "Appending Labels" on page 75

- "Insert All Labels" on page 76

- "Delete All Labels" on page 76

- "Searching for Labels" on page 71

- "Setting Column Color" on page 77

- "Adjusting Column Width" on page 77

- "Rearranging the Label Order" on page 78

- "Setting the Numeric Base" on page 78

- "Setting the Label Font Size" on page 76

## Creating and Inserting New Labels

## **Creating New Labels in Format**

You create labels in Format to uniquely identify groups of assigned pod bits (see page 72) that have a common purpose or identity. Inserting and assigning labels are part of the mapping process (see page 13) for your application.

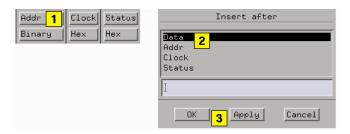

- 1. Right-click the label where you want to insert the new label, then select *Insert before* or *Insert after*.

- 2. In the Enter Label Name dialog that appears, type in the new label name. If you do not provide a label name, a default name is assigned.

- 3. Click OK if you are done, or Apply if you have more labels to insert.

## **Working with Labels and Pods**

NOTE:

Duplicate label names are not allowed.

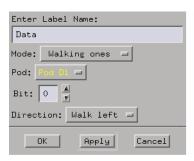

## Mode

If you are creating a series of new labels, you have the option to automatically assign bits in a "walking ones" pattern across the label series. You do this by toggling the *Mode* field to *Walking ones*.

Select the Pod, the starting Bit, and the walk direction. As you enter new label names and click Apply, a single bit is automatically assigned under each new label in a "walking ones" pattern.

# **Deleting Labels**

- 1. Point to the label's name, then press and hold the right mouse button.

- 2. Select *Delete*, then release the mouse button.

See Also

"Clearing Format Labels" on page 71

"Delete All Labels" on page 76

## **Inserting Pre-assigned Labels**

## NOTE:

If labels are not created, assigned bits, and turned on in *Format*, they do not appear in subsequent label operation dialogs in *Sequence* and *Macro*.

- 1. From the *Sequence* or *Macro* tab, right-click the label where you want to insert the new label, then select *Insert Before* or *Insert After*.

- 2. In the Select Label dialog that appears, select the pre-assigned label name to insert.

- 3. Click *OK* if you are done, or *Apply* if you have more labels to insert.

By holding down the *Control key* while using the mouse, you can select multiple label names in a discontinuous manner. By holding down the *Shift key* while using the mouse, you can select multiple label names in a continuous manner.

#### See Also

"Searching for Labels" on page 71

## Renaming Existing Labels

- 1. Under *Format*, right-click the label you want to rename, then select *Rename*.

- 2. In the Rename dialog, type in the new label name.

### **Working with Labels and Pods**

3. Click *OK* if you are done, or *Apply* if you have more labels to rename.

### NOTE:

When you click *Apply*, the next label is automatically highlighted. This lets you rename multiple labels very quickly.

## Reordering a Label's Pod Bits

Use the *Reorder bits* feature to remap the physical probe connections to the interface without changing the actual probe connections. This feature allows the probe tips for each channel to be physically connected where convenient.

- 1. Under the *Format* tab, right-click the label you want to reorder bits on, then select *Reorder bits*.

- 2. Set the bit order by one of the following options:

- To reorder bits individually, for each channel, type the number of the bit you want to map the channel to.

- To arrange the bits sequentially, click the field at the top of the dialog, then select *Default Order*.

- To reverse the order of the bytes, click the field at the top of the dialog, then select *Big Endian Little Endian* mapping. This option is only available for labels that have either 16 or 32 channels.

- 3. Click OK.

## NOTE:

Reordering the bits of a label does not reorder the physical output signals of the channels assigned to that label. The bit order of a label is a displayorientation concept, useful only when entering data values.

# Turning Labels On/Off

Turning labels off prevents output signals from appearing on the associated probe channels. When a label is turned off, it is removed from the *Sequence* and *Macro* areas. However, the label's name and bit

assignments are preserved.

To toggle labels On/Off in Format, right-click the label that you want to modify and toggle the Label On/Off selection.

## **Clearing Format Labels**

The  $Clear Format \ Labels$  command is located under Edit in the Format menu bar. When you select  $Clear Format \ Labels$ , all user-assigned labels are permanently removed, and the default label Lab1 is reset.

# Searching for Labels

In all label selection dialogs, where a list of label names appears, a text entry field is available for a quick search of label names. Simply type in a search string, and all labels that begin with that string appear in the list.

## Swap Pods

The *Swap Pods* command is located under *Edit* in the Format menu bar. When you select *Swap Pods*, the bit assignments for the two designated pods are swapped across all labels.

## **Working with Labels and Pods**

## Clear Pods

The *Clear Pods* command is located under *Edit* in the Format menu bar. When you select *Clear Pods*, all bit assignments for all labels under the designated pod are cleared.

## Assigning Bits to a Label

The bits in a label correspond to the physical pattern generator probe channels. When you run the pattern generator, data is output on all bits (channels) that are assigned to labels. Unassigned bits are inactive.

- An asterisk "\*" indicates an assigned bit.

- A period "." indicates an unassigned bit.

## To Assign Bits

- 1. Select the bit assignment field to the right of the label name you want to define. Each bit assignment field corresponds to the data pod listed above it.

- 2. Click the bits you want to change, toggling them between an asterisk and a period. You can also hold the left mouse button and drag the mouse to

assign several bits at once.

3. When the bits are assigned as desired, close the dialog box.

Right-click in the bit assignment field or dialog to see a shortcut menu for assigning groups of bits.

### NOTE:

Labels can have a maximum of 32 channels assigned to them, however, you cannot assign any single output channel to more than one label.

Bits assigned to a label are numbered from right to left. The least significant assigned bit on the far right is numbered 0. The next assigned bit to the left is numbered 1, and so on. Labels can contain bits that are not consecutive; however, bits are always numbered consecutively within a label.

## Label Polarity

The pattern generator can display each label's data in both positive and negative logic. The default polarity for all labels is positive. To toggle the polarity, left-click the label's polarity field under the *Format* tab.

### NOTE:

Toggling the polarity of a label does not toggle the physical output signal. The polarity of a label is a display orientation concept, useful only when entering data values.

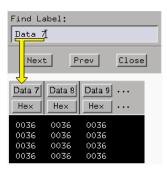

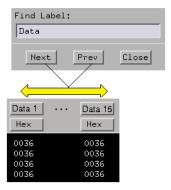

## Finding a label

Access the  $Find\ Label$  feature under Edit in the menu bar of all tabs. The  $Find\ Label$  feature locates specified labels, then displays them.

The search functionality is similar to a text based keyword search. After you type the label name and select Next or Prev, the list of labels is rolled, exposing the label whose text characters, left to right, match

### **Working with Labels and Pods**

the label name entered.

You can search for a complete label name as shown below in example 1, or type just the base name and use the *Next* or *Prev* fields to roll through the list as in example 2.

### Example 1

You have a list of labels named Data1 through Data15. Type the complete name Data7 in the text entry field, then select Next. The label named Data7 appears on the left-most side of the displayed labels.

### Example 2

You have a list of labels named *Data1* through *Data15*. Type only the base name *Data* in the text entry field, then use the *Next* or *Prev* fields to roll the list of labels.

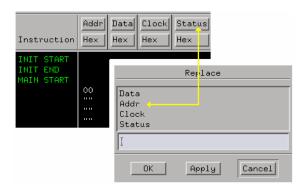

## Replace Labels

The Replace Label command is available in the Sequence and Macro tabs.

- 1. Right-click the label to replace.

- 2. Select Replace.

- 3. From the Select Label dialog that appears, select one or more new labels to replace the existing label. See the mouse tip below.

- 4. Click *OK* if you are done, or *Apply* if you have more labels to replace.

By holding down the *Control key* while using the mouse, you can select multiple label names in a discontinuous manner. By holding down the *Shift key* while using the mouse, you can select multiple label names in a continuous manner.

See Also

"Searching for Labels" on page 71

### **Appending Labels**

The  $Append\ Label\ command$  is located under Edit in the Sequence

#### **Working with Labels and Pods**

and Macro menu bar. The *Append Label* command adds labels to the right of the list of labels in Sequence and Macro.

- 1. In Sequence or Macro, left-click *Edit*, then select *Append Label*.

- 2. From the Select Label dialog that appears, select the new labels to append.

- 3. Click *OK* if you are done, or *Apply* if you have more labels to append.

#### See Also

"Searching for Labels" on page 71

### **Insert All Labels**

The *Insert All Labels* command is located under *Edit* in the Sequence and Macro menu bar. Select this command to insert all valid labels under the Format tab into the sequence.

### Delete All Labels

The  $Delete\ All\ Labels$  command is located under Edit in the Sequence and Macro menu bar. Select this command to delete all assigned labels in the sequence.

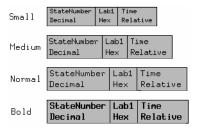

### Setting the Label Font Size

Font settings are global. The font size you select is applied to all text in the display area.

- 1. From the menu bar select *Options*, then select *Font*.

- 2. Select a font size from the list.

### **Example of Font Sizes**

### Adjusting Column Width

- 1. Point to the right edge of the label box.

- 2. Press and hold the *left mouse button*.

- 3. Drag the box edge to the desired width, then release the mouse button.

## Setting Column Color

- 1. Click the Sequence or Macro tab.

- 2. Right-click a label, then select *Change Color*.

- Click the desired color.

- 4. Click OK.

### **Working with Labels and Pods**

### **Setting Default Label Color**

The *Default Label Color* command lets you set the label color for all new labels inserted into either Sequence or Macro.

- 1. Click the Sequence or Macro tab.

- 2. From the menu bar, select *Options*, then select *Default Label Color*.

- 3. From the Default Color dialog that appears, select the desired color.

- 4. Click OK.

### Setting the Numeric Base

- 1. Point to the label's base field, then press and hold the right mouse button.

- 2. Select the desired base type, then release the mouse button.

## Rearranging the Label Order

- 1. *Point* to a label, then press and hold the left mouse button.

- 2. Drag the highlighted label to its new location, then release the mouse button.

## Working with Macro Parameters